以下运算单位为

MemClk

,以

104MHz

为例。

RDF

值运算:

这个值算出来是正确的。

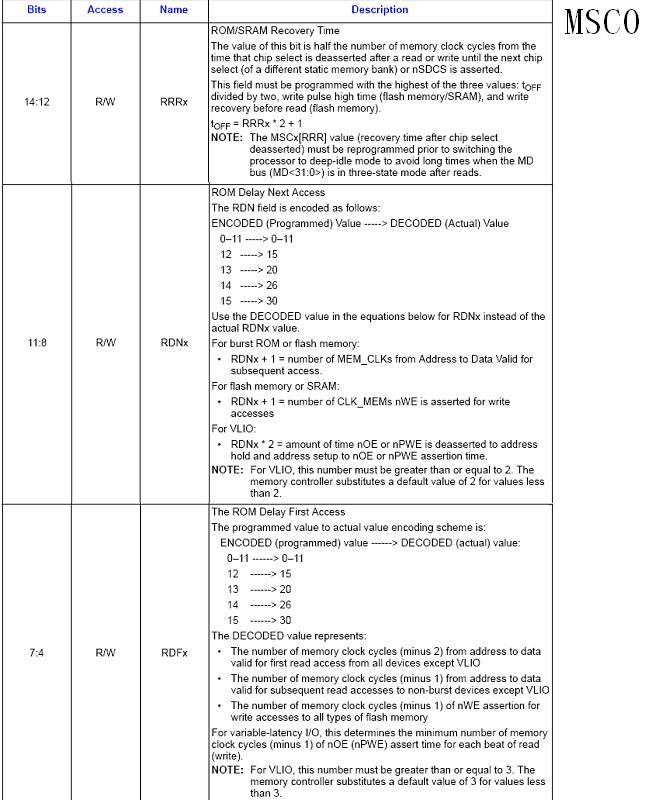

RRR

:

Developer's Manual

中说

RRR

由三个值的最大值决定:

tOFF/2

、

Write pulse high time

和

Write recovery before read

,后两个在

J3 Datesheet

中可以看到。

Write pulse width high=30ns

,

Write recovery before read=35ns

,

tOFF

不知道是什么,找不到。在

Intel StrataFlash Memory(J3) to Intel PXA270 Applications Processor Design Guide

(

301901

)(以下简称

Design Guide

)

中,

RRR0 (MSC0[14:12]) = 0b001 (Read recovery: 1 * 2 + 1 = 3 CLK_MEMs)

,这与

Manual

中不同,否则应该有

RRR>=35ns/10ns

,但这样算与

Design guide

中的不同。且在

DesignGuide

中可以看到,是由

nCS0

为高电平的时间来决定

RRR

的,

但这个值在

Datasheet

中并没有体现出来,就算是以

Addr to Data Valid

时间来算也至少应该是

3

,而不是

Design Guide

中的

1

。

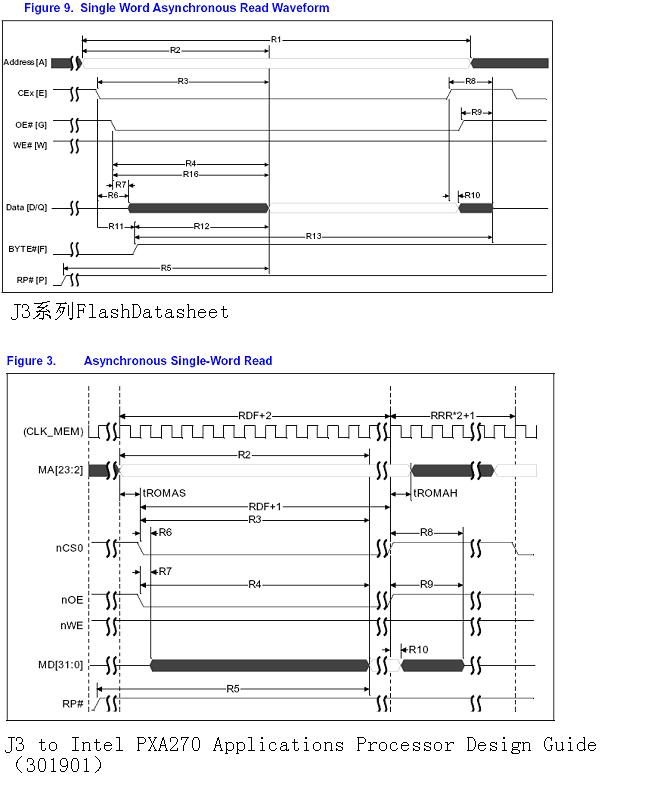

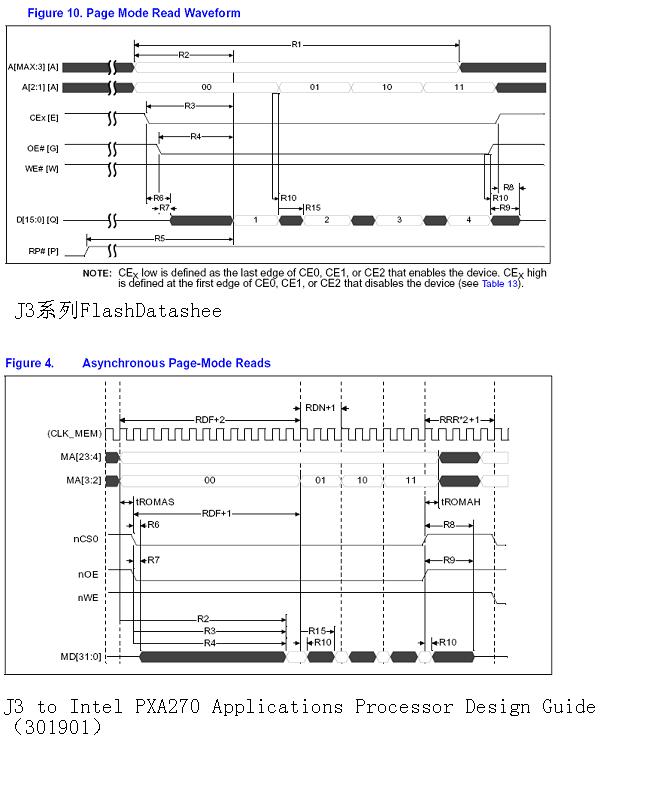

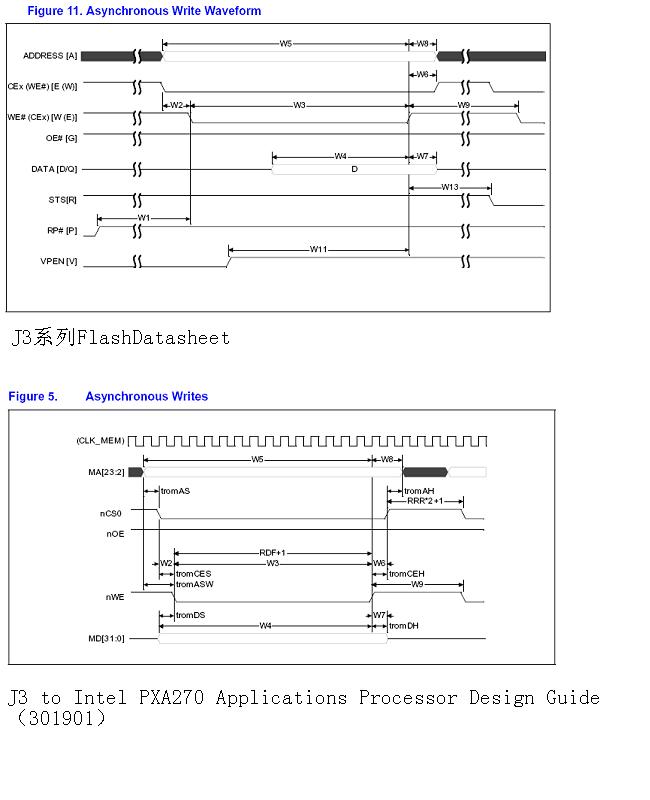

RDN

:

Developer’s Manual

中提到的有两个:

For burst ROM or flash memory:

• RDNx + 1 = number of MEM_CLKs from Address to Data Valid for

subsequent access.

For flash memory or SRAM:

• RDNx + 1 = number of CLK_MEMs nWE is asserted for write

accesses

number of CLK_MEMs nWE is asserted for write

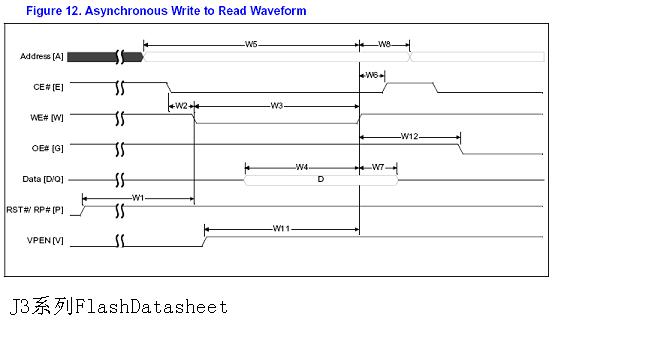

在

Datasheet

中有提到,为

W3

=

70ns

。

Address to Data Valid

我的理解是从地址有效到数据有效时的时间,这样对应到波形图中应该是

R15

=

25ns

,以这个值算的话与

DesignGuide

是差不多的,但

Design Guide

中则指的是

Page mode read

中

Addr

持续时间,这个时间同样在

Datasheet

中没有定义。

相关文件:

AP-769 Intel StrataFlash(R) Memory (J3) to Intel(R) PXA270 Applications Processor Design Guide

30190101.pdf